#### ENGINEERING MATHEMATICS - III

| Sub Code   | : | 10MAT31 | IA Marks          | : | 25  |

|------------|---|---------|-------------------|---|-----|

| Hrs/ Week  | : | 04      | <b>Exam Hours</b> | : | 03  |

| Total Hrs. | : | 52      | <b>Exam Marks</b> | : | 100 |

## **PART-A**

# **UNIT-1**

## **Fourier series**

Convergence and divergence of infinite series of positive terms, definition and illustrative examples\*

Periodic functions, Dirichlet's conditions, Fourier series of periodic functions of period  $2\pi$  and arbitrary period, half range Fourier series. Complex form of Fourier Series. Practical harmonic analysis.

7 Hours

#### **UNIT-2**

### **Fourier Transforms**

Infinite Fourier transform, Fourier Sine and Cosine transforms, properties, Inverse transforms

6 Hours

# **UNIT-3**

## **Application of PDE**

Various possible solutions of one dimensional wave and heat equations, two dimensional Laplace's equation by the method of separation of variables, Solution of all these equations with specified boundary conditions. D'Alembert's solution of one dimensional wave equation.

6 Hours

#### **UNIT-4**

# **Curve Fitting and Optimisation**

Curve fitting by the method of least squares- Fitting of curves of the form y = ax + b,  $y = ax^2 + bx + c$ ,  $y = ae^{bx}$ ,  $y = ax^b$

Optimization: Linear programming, mathematical formulation of linear programming problem (LPP), Graphical method and simplex method.

7 Hours

## **PART-B**

# UNIT-5

# **Numerical Methods - 1**

Numerical Solution of algebraic and transcendental equations: Regula-falsi method, Newton - Raphson method. Iterative methods of solution of a system

of equations: Gauss-seidel and Relaxation methods. Largest eigen value and the corresponding eigen vector by Rayleigh's power method.

6 Hours

## **UNIT-6**

## Numerical Methods – 2

Finite differences: Forward and backward differences, Newton's forward and backward interpolation formulae. Divided differences - Newton's divided difference formula, Lagrange's interpolation formula and inverse interpolation formula.

Numerical integration: Simpson's one-third, three-eighth and Weddle's rules (All formulae/rules without proof)

7 Hours

## **UNIT-7**

#### Numerical Methods - 3

Numerical solutions of PDE – finite difference approximation to derivatives, Numerical solution of two dimensional Laplace's equation, one dimensional heat and wave equations

7 Hours

#### **UNIT-8**

## **Difference Equations and Z-Transorms**

Difference equations: Basic definition; Z-transforms – definition, standard Z-transforms, damping rule, shifting rule, initial value and final value theorems. Inverse Z-transform. Application of Z-transforms to solve difference equations.

6 Hours

Note: \* In the case of illustrative examples, questions are not to be set.

## **Text Books:**

- 1. B.S. Grewal, Higher Engineering Mathematics, Latest edition, Khanna Publishers.

- 2. Erwin Kreyszig, Advanced Engineering Mathematics, Latest edition, Wiley Publications.

## **Reference Books:**

- 1. B.V. Ramana, Higher Engineering Mathematics, Latest edition, Tata Mc. Graw Hill Publications.

- 2. Peter V. O'Neil, Engineering Mathematics, CENGAGE Learning India Pvt Ltd.Publishers.

# ANALOG ELECTRONIC CIRCUITS (Common to EC/TC/EE/IT/BM/ML)

Sub Code

: 10ES32

IA Marks

: 25

Hrs/ Week

: 04

Exam Hours

: 03

Total Hrs.

: 52

Exam Marks

: 100

#### UNIT 1:

**Diode Circuits:** Diode Resistance, Diode equivalent circuits, Transition and diffusion capacitance, Reverse recovery time, Load line analysis, Rectifiers, Clippers and clampers.

6 Hrs

#### **UNIT 2:**

**Transistor Biasing:** Operating point, Fixed bias circuits, Emitter stabilized biased circuits, Voltage divider biased, DC bias with voltage feedback, Miscellaneous bias configurations, Design operations, Transistor switching networks, PNP transistors, Bias stabilization. **6 Hrs**

## **UNIT 3:**

**Transistor at Low Frequencies:** BJT transistor modeling, CE Fixed bias configuration, Voltage divider bias, Emitter follower, CB configuration, Collector feedback configuration, Analysis of circuits r<sub>e</sub> model; analysis of CE configuration using h- parameter model; Relationship between h-parameter model of CE,CC and CE configuration. **7 Hrs**

#### **UNIT 4:**

**Transistor Frequency Response**: General frequency considerations, low frequency response, Miller effect capacitance, High frequency response, multistage frequency effects. **7 Hrs**

## **UNIT 5:**

- (a) General Amplifiers: Cascade connections, Cascode connections, Darlington connections. 3 Hrs

- **(b) Feedback Amplifier:** Feedback concept, Feedback connections type, Practical feedback circuits. Design procedures for the feedback amplifiers.

4 Hrs

# UNIT 6:

**Power Amplifiers**: Definitions and amplifier types, series fed class A amplifier, Transformer coupled Class A amplifiers, Class B amplifier operations, Class B amplifier circuits, Amplifier distortions. Designing of Power amplifiers.

7 Hrs

## **UNIT 7:**

Oscillators: Oscillator operation, Phase shift Oscillator, Wienbridge Oscillator, Tuned Oscillator circuits, Crystal Oscillator. (BJT Version Only) Simple design methods of Oscillators.

6 Hrs

#### **UNIT 8:**

**FET Amplifiers:** FET small signal model, Biasing of FET, Common drain common gate configurations, MOSFETs, FET amplifier networks. **6 Hrs**

## **TEXT BOOK:**

1. **"Electronic Devices and Circuit Theory",** Robert L. Boylestad and Louis Nashelsky, PHI/Pearson Eduication. 9<sup>TH</sup> Edition.

#### **REFERENCE BOOKS:**

- 1. **'Integrated Electronics',** Jacob Millman & Christos C. Halkias, Tata McGraw Hill, 2<sup>nd</sup> Edition, 2010

- "Electronic Devices and Circuits", David A. Bell, PHI, 4<sup>th</sup> Edition, 2004

- 3. "Analog Electronics Circuits: A Simplified Approach", U.B. Mahadevaswamy, Pearson/Saguine, 2007.

# LOGIC DESIGN (Common to EC/TC/EE/IT/BM/ML)

Sub Code

: 10ES33

IA Marks

: 25

Hrs/ Week

: 04

Exam Hours

: 03

Total Hrs.

: 52

Exam Marks

: 100

## UNIT 1:

**Principles of combinational logic-1:** Definition of combinational logic, Canonical forms, Generation of switching equations from truth tables, Karnaugh maps-3, 4 and 5 variables, Incompletely specified functions (Don't Care terms), Simplifying Max term equations. **6 Hrs**

#### **UNIT 2:**

**Principles of combinational Logic-2:** Quine-McCluskey minimization technique- Quine-McCluskey using don't care terms, Reduced Prime Implicant Tables, Map entered variables. **7 Hrs**

## **UNIT 3:**

**Analysis and design of combinational logic - I:** General approach, Decoders-BCD decoders, Encoders. **6 Hrs**

#### **UNIT 4:**

**Analysis and design of combinational logic - II:** Digital multiplexers-Using multiplexers as Boolean function generators. Adders and subtractors-Cascading full adders, Look ahead carry, Binary comparators. Design methods of building blocks of combinational logics.

7 Hrs

### **UNIT 5:**

**Sequential Circuits** – **1:** Basic Bistable Element, Latches, SR Latch, Application of SR Latch, A Switch Debouncer, The  $\overline{S}^{\square} \overline{R}^{\square}$  Latch, The gated SR Latch, The gated D Latch, The Master-Slave Flip-Flops (Pulse-Triggered Flip-Flops): The Master-Slave SR Flip-Flops, The Master-Slave JK Flip-Flop, Edge Triggered Flip-Flop: The Positive Edge-Triggered D Flip-Flop, Negative-Edge Triggered D Flip-Flop. **7 Hrs**

## UNIT 6:

**Sequential Circuits – 2:** Characteristic Equations, Registers, Counters - Binary Ripple Counters, Synchronous Binary counters, Counters based on Shift Registers, Design of a Synchronous counters, Design of a Synchronous Mod-6 Counter using clocked JK Flip-Flops Design of a Synchronous Mod-6 Counter using clocked D, T, or SR Flip-Flops **7 Hrs**

### **UNIT 7:**

**Sequential Design - I:** Introduction, Mealy and Moore Models, State Machine Notation, Synchronous Sequential Circuit Analysis and Design.

6 Hrs

## **UNIT 8:**

Sequential Design - II: Construction of state Diagrams, Counter Design.

6 Hrs

## **TEXT BOOKS:**

- 1. "Digital Logic Applications and Design", John M Yarbrough, Thomson Learning, 2001.

- 2. **"Digital Principles and Design ",** Donald D Givone, Tata McGraw Hill Edition, 2002.

## **REFERENCE BOOKS:**

- 1. **"Fundamentals of logic design"**, Charles H Roth, Jr; Thomson Learning, 2004.

- 2. "Logic and computer design Fundamentals", Mono and Kim, Pearson, Second edition, 2001.

- 3. "Logic Design", Sudhakar Samuel, Pearson/Saguine, 2007

# NETWORK ANALYSIS (Common to EC/TC/EE/IT/BM/ML)

| Sub Code   | : | 10ES34 | IA Marks   | : | 25  |

|------------|---|--------|------------|---|-----|

| Hrs/ Week  | : | 04     | Exam Hours | : | 03  |

| Total Hrs. | : | 52     | Exam Marks | : | 100 |

## **UNIT 1:**

**Basic Concepts**: Practical sources, Source transformations, Network reduction using Star – Delta transformation, Loop and node analysis With linearly dependent and independent sources for DC and AC networks, Concepts of super node and super mesh.

7 Hrs

## **UNIT 2:**

**Network Topology:** Graph of a network, Concept of tree and co-tree, incidence matrix, tie-set, tie-set and cut-set schedules, Formulation of equilibrium equations in matrix form, Solution of resistive networks, Principle of duality.

7 Hrs

## **UNIT 3:**

**Network Theorems – 1:** Superposition, Reciprocity and Millman's theorems. **6 Hrs**

## **UNIT 4:**

## **Network Theorems - II:**

Thevinin's and Norton's theorems; Maximum Power transfer theorem . 6 Hrs

**UNIT 5: Resonant Circuits:** Series and parallel resonance, frequency-response of series and Parallel circuits, Q –factor, Bandwidth.

#### 7 Hrs

#### UNIT 6:

**Transient behavior and initial conditions**: Behavior of circuit elements under switching condition and their Representation, evaluation of initial and final conditions in RL, RC and RLC circuits for AC and DC excitations.

7 Hrs

## **UNIT 7:**

**Laplace Transformation & Applications**: Solution of networks, step, ramp and impulse responses, waveform Synthesis. **6 Hrs**

#### **UNIT 8:**

**Two port network parameters:** Definition of z, y, h and transmission parameters, modeling with these parameters, relationship between parameters sets.

6 Hrs

## **TEXT BOOKS:**

- 1. **"Network Analysis",** M. E. Van Valkenburg, PHI / Pearson Education, 3<sup>rd</sup> Edition. Reprint 2002.

- "Networks and systems", Roy Choudhury, 2<sup>nd</sup> edition, 2006 re-print, New Age International Publications.

# **REFERENCE BOOKS:**

- **1. "Engineering Circuit Analysis",** Hayt, Kemmerly and DurbinTMH 7<sup>th</sup> Edition, 2010

- **2. "Basic Engineering Circuit Analysis"**, J. David Irwin / R. Mark Nelms, John Wiley, 8<sup>th</sup> ed, 2006.

- **3." Fundamentals of Electric Circuits"**, Charles K Alexander and Mathew N O Sadiku. Tata McGraw-Hill. 3 ed. 2009.

# ELECTRONIC INSTRUMENTATION (Common to EC/TC/IT/BM/ML)

Sub Code

: 10IT35

IA Marks

: 25

Hrs/ Week

: 04

Exam Hours

: 03

Total Hrs.

: 52

Exam Marks

: 100

#### **UNIT - 1:**

#### Introduction

- (a) **Measurement Errors:** Gross errors and systematic errors, Absolute and relative errors, Accuracy, Precision, Resolution and Significant figures.

- **(b) Voltmeters and Multimeters** Introduction, Multirange voltmeter, Extending voltmeter ranges, Loading, AC voltmeter using Rectifiers Half wave and full wave, Peak responding and True RMS voltmeters.

3 + 4 Hrs

## **UNIT - 2:**

## **Digital Instruments**

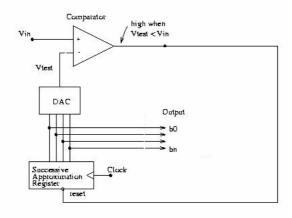

Digital Voltmeters – Introduction, DVM's based on V – T, V – F and Successive approximation principles, Resolution and sensitivity, General specifications, Digital Multi-meters, Digital frequency meters, Digital measurement of time.

6 Hrs

# **UNIT - 3:**

## Oscilloscopes

Introduction, Basic principles, CRT features, Block diagram and working of each block, Typical CRT connections, Dual beam and dual trace CROs, Electronic switch.

6 Hrs

## **UNIT - 4:**

# **Special Oscilloscopes**

Delayed time-base oscilloscopes, Analog storage, Sampling and Digital storage oscilloscopes. **6 Hrs**

## **UNIT - 5:**

#### **Signal Generators**

Introduction, Fixed and variable AF oscillator, Standard signal generator, Laboratory type signal generator, AF sine and Square wave generator, Function generator, Square and Pulse generator, Sweep frequency generator, Frequency synthesizer.

6 Hrs

### **UNIT - 6:**

# Measurement of resistance, inductance and capacitance

Whetstone's bridge, Kelvin Bridge; AC bridges, Capacitance Comparison Bridge, Maxwell's bridge, Wein's bridge, Wagner's earth connection

5 Hrs

## **UNIT - 7:**

Transducers - I

Introduction, Electrical transducers, Selecting a transducer, Resistive transducer, Resistive position transducer, Strain gauges, Resistance thermometer, Thermistor, Inductive transducer, Differential output transducers and LVDT.

6 Hrs

## **UNIT - 8:**

## **Miscellaneous Topics**

- (a) **Transducers II** –Piezoelectric transducer, Photoelectric transducer, Photovoltaic transducer, Semiconductor photo devices, Temperature transducers-RTD, Thermocouple .

- **(b) Display devices:** Digital display system, classification of display, Display devices, LEDs, LCD displays.

- (c) Bolometer and RF power measurement using Bolometer

- (d) Introduction to Signal conditioning.

- (e) Introduction to LabView.

10 Hrs

## **TEXT BOOKS:**

- 1. "Electronic Instrumentation", H. S. Kalsi, TMH, 3<sup>rd</sup> 2010

- 2. **"Electronic Instrumentation and Measurements"**, David A Bell, PHI / Pearson Education, 2006.

#### **REFERENCE BOOKS:**

- 1. **"Principles of measurement systems"**, John P. Beately, 3<sup>rd</sup> Edition, Pearson Education, 2000

- 2. "Modern electronic instrumentation and measuring techniques", Cooper D & A D Helfrick, PHI, 1998.

- 3. **Electronics & electrical measurements,** A K Sawhney, , Dhanpat Rai & sons, 9<sup>th</sup> edition.

# FIELD THEORY (Common to EC/TC/ML/EE)

| Sub Code   | : | 10ES36 | IA Marks   | : | 25  |

|------------|---|--------|------------|---|-----|

| Hrs/ Week  | : | 04     | Exam Hours | : | 03  |

| Total Hrs. | : | 52     | Exam Marks | : | 100 |

# UNIT 1:

- a. Coulomb's Law and electric field intensity: Experimental law of Coulomb, Electric field intensity, Field due to continuous volume charge distribution, Field of a line charge.

3 Hrs

- **b. Electric flux density, Gauss' law and divergence:** Electric flux density, Gauss' law, Divergence, Maxwell's First equation(Electrostatics), vector

## **UNIT 2:**

- a. Energy and potential: Energy expended in moving a point charge in an electric field, The line integral, Definition of potential difference and Potential, The potential field of a point charge and system of charges, Potential gradient, Energy density in an electrostatic field. 4 Hrs

- b. Conductors, dielectrics and capacitance: Current and current density,

Continuity of current, metallic conductors, Conductor properties and

boundary conditions, boundary conditions for perfect Dielectrics, capacitance

and examples.

4 Hrs

## **UNIT 3:**

**Poisson's and Laplace's equations:** Derivations of Poisson's and Laplace's Equations, Uniqueness theorem, Examples of the solutions of Laplace's and Poisson's equations.

6 Hrs

## **UNIT 4:**

The steady magnetic field: Biot-Savart law, Ampere's circuital law, Curl, Stokes' theorem, magnetic flux and flux density, scalar and Vector magnetic potentials.

6 Hrs

#### **UNIT 5:**

- a. Magnetic forces: Force on a moving charge and differential current element, Force between differential current elements, Force and torque on a closed circuit.

4 Hrs

- b. Magnetic materials and inductance: Magnetization and permeability,

Magnetic boundary conditions, Magnetic circuit, Potential energy and forces on magnetic materials, Inductance and Mutual Inductance.

4 Hrs

## UNIT 6:

Time varying fields and Maxwell's equations: Faraday's law, displacement current, Maxwell's equation in point and Integral form, retarded potentials.

6 Hrs

### **UNIT 7:**

**Uniform plane wave:** Wave propagation in free space and dielectrics, Poynting's theorem and wave power, propagation in good conductors – (skin effect).

6 Hrs

# **UNIT 8:**

Plane waves at boundaries and in dispersive media: Reflection of uniform plane waves at normal incidence, SWR, Plane wave propagation in general directions.

6 Hrs

## **TEXT BOOK:**

**1. "Engineering Electromagnetics",** William H Hayt Jr. and John A Buck, Tata McGraw-Hill, 7<sup>th</sup> edition, 2006

# **REFERENCE BOOKS:**

- 1. **"Electromagnetics with Applications"**, John Krauss and Daniel A Fleisch, McGraw-Hill, 5<sup>th</sup> edition, 1999

- "Electromagnetic Waves And Radiating Systems," Edward C. Jordan and Keith G Balmain, Prentice – Hall of India / Pearson Education, 2<sup>nd</sup> edition, 1968.Reprint 2002

- 3. **"Field and Wave Electromagnetics"**, David K Cheng, Pearson Education Asia, 2<sup>nd</sup> edition, 1989, Indian Reprint 2001.

# ANALOG ELECTRONICS LAB (Common to EC/TC/EE/IT/BM/ML)

| Sub Code   | : | 10ESL37 | IA Marks          | : | 25 |

|------------|---|---------|-------------------|---|----|

| Hrs/ Week  | : | 03      | Exam Hours        | : | 03 |

| Total Hrs. | : |         | <b>Exam Marks</b> | : | 50 |

**NOTE:** Use the Discrete components to test the circuits. LabView can be used for the verification and testing along with the above.

- 1. Wiring of RC coupled Single stage FET & BJT amplifier and determination of the gain-frequency response, input and output impedances.

- 2. Wiring of BJT Darlington Emitter follower with and without bootstrapping and determination of the gain, input and output impedances (Single circuit) (One Experiment)

- 3. Wiring of a two stage BJT Voltage series feed back amplifier and determination of the gain, Frequency response, input and output impedances with and without feedback (One Experiment)

- 4. Wiring and Testing for the performance of BJT-RC Phase shift Oscillator for  $f_0 \! \leq \! 10 \text{ KHz}$

- 5. Testing for the performance of BJT Hartley & Colpitts Oscillators  $\,$  for RF range  $f_0\!\ge\!100KHz.$

- 6. Testing for the performance of BJT -Crystal Oscillator for  $f_0 > 100 \text{ KHz}$  7 Testing of Diode clipping (Single/Double ended) circuits for peak clipping, peak detection

- 8. Testing of Clamping circuits: positive clamping /negative clamping.

- 9. Testing of a transformer less Class B push pull power amplifier and determination of its conversion efficiency.

- 10. Testing of Half wave, Full wave and Bridge Rectifier circuits with and without Capacitor filter. Determination of ripple factor, regulation and efficiency

- 11. Verification of Thevinin's Theorem and Maximum Power Transfer theorem for DC Circuits.

- 12. Characteristics of Series and Parallel resonant circuits.

# LOGIC DESIGN LAB (Common to EC/TC/EE/IT/BM/ML)

| Sub Code   | : | 10ESL38 | IA Marks   | : | 25 |

|------------|---|---------|------------|---|----|

| Hrs/ Week  | : | 03      | Exam Hours | : | 03 |

| Total Hrs. | : |         | Exam Marks | : | 50 |

**NOTE:** Use discrete components to test and verify the logic gates. LabView can be used for designing the gates along with the above.

- 1. Simplification, realization of Boolean expressions using logic gates/Universal gates.

- Realization of Half/Full adder and Half/Full Subtractors using logic gates.

- 3. (i) Realization of parallel adder/Subtractors using 7483 chip (ii) BCD to Excess-3 code conversion and vice versa.

- 4. Realization of Binary to Gray code conversion and vice versa

- 5. MUX/DEMUX use of 74153, 74139 for arithmetic circuits and code converter.

- Realization of One/Two bit comparator and study of 7485 magnitude comparator.

- 7. Use of a) Decoder chip to drive LED display and b) Priority encoder.

- 8. Truth table verification of Flip-Flops: (i) JK Master slave (ii) T type and (iii) D type.

- 9. Realization of 3 bit counters as a sequential circuit and MOD N counter design (7476, 7490, 74192, 74193).

- 10. Shift left; Shift right, SIPO, SISO, PISO, PIPO operations using 74S95.11. Wiring and testing Ring counter/Johnson counter.12. Wiring and testing of Sequence generator.

# **ENGINEERING MATHEMATICS – IV**

| Sub Code   | : | 10MAT41 | IA Marks          | : | 25  |

|------------|---|---------|-------------------|---|-----|

| Hrs/ Week  | : | 04      | Exam Hours        | : | 03  |

| Total Hrs. | : | 52      | <b>Exam Marks</b> | : | 100 |

# **PART-A**

# **UNIT-1**

## **Numerical Methods-1**

Numerical solution of ordinary differential equations of first order and first degree; Picard's method, Taylor's series method, modified Euler's method, Runge-kutta method of fourth-order. Milne's and Adams - Bashforth predictor and corrector methods (No derivations of formulae).

6 Hours

# **UNIT-2**

## Numerical Methods – 2

Numerical solution of simultaneous first order ordinary differential equations: Picard's method, Runge-Kutta method of fourth-order.

Numerical solution of second order ordinary differential equations: Picard's method, Runge-Kutta method and Milne's method.

6 Hours

## **UNIT-3**

# Complex variables - 1

Function of a complex variable, Analytic functions-Cauchy-Riemann equations in cartesian and polar forms. Properties of analytic functions. Application to flow problems- complex potential, velocity potential, equipotential lines, stream functions, stream lines.

7 Hours

# UNIT-4

## Complex variables - 2

Conformal Transformations: Bilinear Transformations. Discussion of Transformations:  $w = z^2$ ,  $w = e^z$ ,  $w = z + (a^2/z)$ . Complex line integrals- Cauchy's theorem and Cauchy's integral formula.

7 Hours

## **PART-B**

# **UNIT-5**

# **Special Functions**

Solution of Laplace equation in cylindrical and spherical systems leading Bessel's and Legendre's differential equations, Series solution of Bessel's differential equation leading to Bessel function of first kind. Orthogonal property of Bessel functions. Series solution of Legendre's differential equation leading to Legendre polynomials, Rodrigue's formula.

7 Hours

# **UNIT-6**

## **Probability Theory - 1**

Probability of an event, empherical and axiomatic definition, probability associated with set theory, addition law, conditional probability, multiplication law, Baye's theorem.

6 Hours

## **UNIT-7**

# **Probability Theory-2**

Random variables (discrete and continuous), probability density function, cumulative density function. Probability distributions – Binomial and Poisson distributions; Exponential and normal distributions.

7 Hours

## **UNIT-**

## **Sampling Theory**

Sampling, Sampling distributions, standard error, test of hypothesis for means, confidence limits for means, student's t-distribution. Chi -Square distribution as a test of goodness of fit

6 Hours

### **Text Books:**

- 1. B.S. Grewal, Higher Engineering Mathematics, Latest edition, Khanna Publishers

- 2. Erwin Kreyszig, Advanced Engineering Mathematics, Latest edition, Wiley Publications.

### **Reference Book:**

- 1. B.V. Ramana, Higher Engineering Mathematics, Latest edition, Tata Mc. Graw Hill Publications.

- 2. Peter V. O'Neil, Engineering Mathematics, CENGAGE Learning India Pvt Ltd.Publishers.

# MICROCONTROLLERS (Common to EC/TC/EE/IT/BM/ML)

| Sub Code   | : | 10ES42 | IA Marks   | : | 25  |

|------------|---|--------|------------|---|-----|

| Hrs/ Week  | : | 04     | Exam Hours | : | 03  |

| Total Hrs. | : | 52     | Exam Marks | : | 100 |

#### **UNIT 1**:

Microprocessors and microcontroller. Introduction, Microprocessors and Microcontrollers, RISC & CISC CPU Architectures, Harvard & Von-Neumann CPU architecture, Computer software.

The 8051 Architecture: Introduction, Architecture of 8051, Pin diagram of 8051, Memory organization, External Memory interfacing, Stacks.

6 Hrs

## **UNIT 2:**

Addressing Modes: Introduction, Instruction syntax, Data types, Subroutines, Addressing modes: Immediate addressing, Register addressing, Direct addressing, Indirect addressing, relative addressing, Absolute addressing, Long addressing, Indexed addressing, Bit inherent addressing, bit direct addressing.

Instruction set: Instruction timings, 8051 instructions: Data transfer instructions, Arithmetic instructions, Logical instructions, Branch instructions, Subroutine instructions, Bit manipulation instruction.

6 Hrs. UNIT 3:

8051 programming: Assembler directives, Assembly language programs and Time delay calculations. **6 Hrs**

## UNIT 4:

8051 Interfacing and Applications: Basics of I/O concepts, I/O Port Operation, Interfacing 8051 to LCD, Keyboard, parallel and serial ADC, DAC, Stepper motor interfacing and DC motor interfacing and programming

7 Hrs

#### **UNIT 5:**

8051 Interrupts and Timers/counters: Basics of interrupts, 8051 interrupt structure, Timers and Counters, 8051 timers/counters, programming 8051 timers in assembly and C . **6 Hrs**

#### UNIT 6:

8051 Serial Communication: Data communication, Basics of Serial Data Communication, 8051 Serial Communication, connections to RS-232, Serial communication Programming in assembly and C.

8255A Programmable Peripheral Interface:, Architecture of 8255A, I/O addressing,, I/O devices interfacing with 8051 using 8255A. 6 **Hrs**

Course Aim – The MSP430 microcontroller is ideally suited for development of low-power embedded systems that must run on batteries for many years. There are also applications where MSP430 microcontroller must operate on energy harvested from the environment. This is possible due to the ultra-low power operation of MSP430 and the fact that it provides a complete system solution including a RISC CPU, flash memory, on-chip data converters and on-chip peripherals.

#### **UNIT 7:**

Motivation for MSP430microcontrollers – Low Power embedded systems, On-chip peripherals (analog and digital), low-power RF capabilities. Target applications (Single-chip, low cost, low power, high performance system design).

2 Hrs

MSP430 RISC CPU architecture, Compiler-friendly features, Instruction set, Clock system, Memory subsystem. Key differentiating factors between different MSP430 families.

2 Hrs

Introduction to Code Composer Studio (CCS v4). Understanding how to use CCS for Assembly, C, Assembly+C projects for MSP430 microcontrollers. Interrupt programming.

3 Hrs

**Digital I/O – I/O ports** programming using C and assembly, Understanding the muxing scheme of the MSP430 pins. **2 Hrs**

#### **UNIT 8**:

On-chip peripherals. Watchdog Timer, Comparator, Op-Amp, Basic Timer, Real Time Clock (RTC), ADC, DAC, SD16, LCD, DMA. 2 Hrs Using the Low-power features of MSP430. Clock system, low-power modes, Clock request feature, Low-power programming and Interrupt. 2 Hrs Interfacing LED, LCD, External memory. Seven segment LED modules interfacing. Example – Real-time clock. 2 Hrs

**Case Studies of applications of MSP430** - Data acquisition system, Wired Sensor network, Wireless sensor network with Chipcon RF interfaces.

3 Hrs

#### **TEXT BOOKS:**

- 1. "The 8051 Microcontroller and Embedded Systems using assembly and C"-, Muhammad Ali Mazidi and Janice Gillespie Mazidi and Rollin D. McKinlay; PHI, 2006 / Pearson, 2006

- 2. **"MSP430 Microcontroller Basics",** John Davies, Elsevier, 2010 (Indian edition available)

# **REFERENCE BOOKS:**

- "The 8051 Microcontroller Architecture, Programming & Applications", 2e Kenneth J. Ayala; Penram International, 1996 / Thomson Learning 2005.

- 2. "The 8051 Microcontroller", V.Udayashankar and MalikarjunaSwamy, TMH, 2009

- 3. **MSP430 Teaching CD-ROM,** Texas Instruments, 2008 (can be requested **http://www.uniti.in**)

- 4. **Microcontrollers: Architecture, Programming, Interfacing and System Design"**, Raj Kamal, "Pearson Education, 2005

# CONTROL SYSTEMS (Common to EC/TC/EE/IT/BM/ML)

Sub Code

: 10ES43

IA Marks

: 25

Hrs/ Week

: 04

Exam Hours

: 03

Total Hrs.

: 52

Exam Marks

: 100

## UNIT 1:

**Modeling of Systems:** Introduction to Control Systems, Types of Control Systems, Effect of Feedback Systems, Differential equation of Physical Systems -Mechanical systems, Friction, Translational systems (Mechanical accelerometer, systems excluded), Rotational systems, Gear trains, Electrical systems, Analogous systems. **7 Hrs**

# UNIT 2:

**Block diagrams and signal flow graphs:** Transfer functions, Block diagram algebra, Signal Flow graphs (State variable formulation excluded), **6 Hrs**

## **UNIT 3:**

**Time Response of feed back control systems**: Standard test signals, Unit step response of First and second order systems, Time response specifications, Time response specifications of second order systems, steady

state errors and error constants. Introduction to PID Controllers(excluding design)7 Hrs

#### **UNIT 4:**

**Stability analysis:** Concepts of stability, Necessary conditions for Stability, Routh- stability criterion, Relative stability analysis; More on the Routh stability criterion.

6 Hrs

## **UNIT 5:**

**Root–Locus Techniques**: Introduction, The root locus concepts, Construction of root loci. 6 Hrs

#### UNIT 6:

**Frequency domain analysis:** Correlation between time and frequency response, Bode plots, Experimental determination of transfer functions, Assessment of relative stability using Bode Plots. Introduction to lead, lag and lead-lag compensating networks (excluding design). **7 Hrs**

#### **UNIT 7:**

**Stability in the frequency domain:** Introduction to Polar Plots, (Inverse Polar Plots excluded) Mathematical preliminaries, Nyquist Stability criterion, Assessment of relative stability using Nyquist criterion, (Systems with transportation lag excluded). **7 Hrs**

#### **UNIT 8:**

**Introduction to State variable analysis:** Concepts of state, state variable and state models for electrical systems, Solution of state equations. **6 Hrs**

## **TEXT BOOK:**

**1. J. Nagarath and M.Gopal**, "Control Systems Engineering", New Age International (P) Limited, Publishers, Fourth edition – 2005

#### REFERENCE BOOKS:

- "Modern Control Engineering ", K. Ogata, Pearson Education Asia/ PHI, 4<sup>th</sup> Edition, 2002.

- 2. "Automatic Control Systems", Benjamin C. Kuo, John Wiley India Pvt. Ltd., 8<sup>th</sup> Edition, 2008.

- 3. **"Feedback and Control System"**, Joseph J Distefano III et al., Schaum's Outlines, TMH, 2<sup>nd</sup> Edition 2007.

# SIGNALS & SYSTEMS (Common to EC/TC/IT/BM/ML)

| Sub Code   | : | 10EC44 | IA Marks   | : | 25  |

|------------|---|--------|------------|---|-----|

| Hrs/ Week  | : | 04     | Exam Hours | : | 03  |

| Total Hrs. | : | 52     | Exam Marks | : | 100 |

### UNIT 1:

**Introduction**: Definitions of a signal and a system, classification of signals, basic Operations on signals, elementary signals, Systems viewed as Interconnections of operations, properties of systems.

6 Hrs

#### UNIT 2:

Time-domain representations for LTI systems – 1: Convolution, impulse response representation, Convolution Sum and Convolution Integral.

6 Hrs

#### UNIT 3:

**Time-domain representations for LTI systems – 2:** Properties of impulse response representation, Differential and difference equation Representations, Block diagram representations. **7 Hrs**

### **UNIT 4:**

Fourier representation for signals – 1: Introduction, Discrete time and continuous time Fourier series (derivation of series excluded) and their properties.

7 Hrs

#### **UNIT 5:**

**Fourier representation for signals – 2:** Discrete and continuous Fourier transforms(derivations of transforms are excluded) and their properties.

6 Hrs

# UNIT 6:

**Applications of Fourier representations:** Introduction, Frequency response of LTI systems, Fourier transform representation of periodic signals, Fourier transform representation of discrete time signals. Sampling theorm and Nyquist rate.

7 Hrs

## **UNIT 7:**

**Z-Transforms** – **1:** Introduction, Z – transform, properties of ROC, properties of Z – transforms, inversion of Z – transforms. **7 Hrs**

## **UNIT 8:**

Z-transforms - 2: Transform analysis of LTI Systems, unilateral Z-

## **TEXT BOOK**

- **1. Simon Haykin,** "Signals and Systems", John Wiley India Pvt. Ltd., 2<sup>nd</sup> Edn, 2008.

- **2. Michael Roberts,** "Fundamentals of Signals & Systems", 2<sup>nd</sup> ed, Tata McGraw-Hill, 2010

## **REFERENCE BOOKS:**

- 1. **Alan V Oppenheim, Alan S, Willsky and A Hamid Nawab,** "Signals and Systems" Pearson Education Asia / PHI, 2<sup>nd</sup> edition, 1997. Indian Reprint 2002

- 2. **H. P Hsu, R. Ranjan**, "Signals and Systems", Scham's outlines, TMH, 2006

- 3. **B. P. Lathi**, "Linear Systems and Signals", Oxford University Press, 2005

- 4. **Ganesh Rao and Satish Tunga**, "Signals and Systems", Pearson/Sanguine Technical Publishers, 2004

# FUNDAMENTALS OF HDL (Common to EC/TC/IT/BM/ML)

| Sub Code   | : | 10EC45 | IA Marks   | : | 25  |

|------------|---|--------|------------|---|-----|

| Hrs/ Week  | : | 04     | Exam Hours | : | 03  |

| Total Hrs. | : | 52     | Exam Marks | : | 100 |

## UNIT 1:

**Introduction:** Why HDL? , A Brief History of HDL, Structure of HDL Module, Operators, Data types, Types of Descriptions, simulation and synthesis, Brief comparison of VHDL and Verilog **7 Hrs**

#### UNIT 2

**Data –Flow Descriptions:** Highlights of Data-Flow Descriptions, Structure of Data-Flow Description, Data Type – Vectors. **6 Hrs**

#### LINIT 3

**Behavioral Descriptions:** Behavioral Description highlights, structure of HDL behavioral Description, The VHDL variable –Assignment Statement, sequential statements.

6 Hrs

## **UNIT 4:**

**Structural Descriptions**: Highlights of structural Description, Organization of the structural Descriptions, Binding, state Machines, Generate, Generic, and Parameter statements. **7 Hrs**

**UNIT 5: Procedures, Tasks, and Functions:** Highlights of Procedures, tasks, and Functions, Procedures and tasks, Functions.

Advanced HDL Descriptions: File Processing, Examples of File Processing

7 Hrs

#### UNIT 6:

**Mixed –Type Descriptions:** Why Mixed-Type Description? VHDL User-Defined Types, VHDL Packages, Mixed-Type Description examples

6 Hrs

## **UNIT 7:**

**Mixed – Language Descriptions:** Highlights of Mixed-Language Description, How to invoke One language from the Other, Mixed-language Description Examples, Limitations of Mixed-Language Description. **7 Hrs UNIT 8:**

**Synthesis Basics:** Highlights of Synthesis, Synthesis information from Entity and Module, Mapping Process and Always in the Hardware Domain. **6 Hrs**

## **TEXT BOOKS:**

HDL Programming (VHDL and Verilog)- Nazeih M.Botros- John Weily India Pvt. Ltd. 2008.

## **REFERENCE BOOKS:**

- 1. **Fundamentals of HDL** Cyril P.R. Pearson/Sanguin 2010.

- 2. VHDL -Douglas perry-Tata McGraw-Hill

- 3. A Verilog HDL Primer- J.Bhaskar BS Publications

- 4. Circuit Design with VHDL-Volnei A.Pedroni-PHI

# LINEAR IC's & APPLICATIONS (Common to EC/TC/IT/BM/ML)

Sub Code

: 10EC46

IA Marks

: 25

Hrs/ Week

: 04

Exam Hours

: 03

Total Hrs.

: 52

Exam Marks

: 100

#### **UNIT 1:**

Operational Amplifier Fundamentals: Basic Op-Amp circuit, Op-Amp parameters – Input and output voltage, CMRR and PSRR, offset voltages and currents, Input and output impedances, Slew rate and Frequency limitations; Op-Amps as DC Amplifiers- Biasing Op-Amps, Direct coupled -Voltage Followers, Non-inverting Amplifiers, Inverting amplifiers, Summing amplifiers, Difference amplifier. 7 Hrs

#### UNIT 2:

**Op-Amps as AC Amplifiers:** Capacitor coupled Voltage Follower, High input impedance - Capacitor coupled Voltage Follower, Capacitor coupled Non-inverting Amplifiers, High input impedance - Capacitor coupled Non-inverting Amplifiers, Capacitor coupled Inverting amplifiers, setting the upper cut-off frequency, Capacitor coupled Difference amplifier, Use of a single polarity power supply. **7 Hrs**

#### **UNIT 3:**

**Op-Amps frequency response and compensation:** Circuit stability, Frequency and phase response, Frequency compensating methods, Band width, Slew rate effects,  $Z_{in}$  Mod compensation, and circuit stability precautions. **6 Hrs**

#### **UNIT 4:**

**OP-AMP Applications:** Voltage sources, current sources and current sinks, Current amplifiers, instrumentation amplifier, precision rectifiers, Limiting circuits. **6 Hrs**

## UNIT 5:

**More applications:** Clamping circuits, Peak detectors, sample and hold circuits, V to I and I to V converters, Log and antilog amplifiers, Multiplier and divider, Triangular / rectangular wave generators, Wave form generator design, phase shift oscillator, Wein bridge oscillator. **7 Hrs**

#### **UNIT 6:**

**Non-linear circuit applications:** crossing detectors, inverting Schmitt trigger circuits, Monostable & Astable multivibrator, Active Filters –First and second order Low pass & High pass filters.

6 Hrs

## **UNIT 7:**

**Voltage Regulators:** Introduction, Series Op-Amp regulator, IC Voltage regulators, 723 general purpose regulator, Switching regulator. **6 Hrs**

# **UNIT 8:**

Other Linear IC applications: 555 timer - Basic timer circuit, 555 timer used as a stable and monostable multivibrator, Schmitt trigger; PLL-operating principles, Phase detector / comparator, VCO; D/A and A/ D converters - Basic DAC Techniques, AD converters. 7 Hrs

## **TEXT BOOKS:**

- 1. "Operational Amplifiers and Linear IC's", David A. Bell, 2<sup>nd</sup> edition, PHI/Pearson, 2004

- 2. **"Linear Integrated Circuits"**, D. Roy Choudhury and Shail B. Jain, 2<sup>nd</sup> edition, Reprint 2006, New Age International

## **REFERENCE BOOKS:**

- **1. "Opamps- Design, Applications and Trouble Shooting",** Terrell, Elsevier, 3<sup>rd</sup> ed. 2006.

- **2. "Operational Amplifiers",** George Clayton and Steve Winder, Elsever

- 5<sup>th</sup> ed., 2008

- 3. "Operational Amplifiers and Linear Integrated Circuits", Robert.

- F. Coughlin & Fred.F. Driscoll, PHI/Pearson, 2006

- 4. "Design with Operational Amplifiers and Analog Integrated Circuits", Sergio Franco, TMH, 3e, 2005

# MICROCONTROLLERS LAB (Common to EC/TC/EE/IT/BM/ML)

| Sub Code   | : | 10ESL47 | IA Marks          | : | 25 |

|------------|---|---------|-------------------|---|----|

| Hrs/ Week  | : | 03      | Exam Hours        | : | 03 |

| Total Hrs. | : | 42      | <b>Exam Marks</b> | : | 50 |

## I. PROGRAMMING

1. Data Transfer - Block move, Exchange, Sorting, Finding largest element in an array.

- 2. Arithmetic Instructions Addition/subtraction, multiplication and division, square, Cube (16 bits Arithmetic operations bit addressable).

- 3. Counters.

- 4. Boolean & Logical Instructions (Bit manipulations).

- 5. Conditional CALL & RETURN.

- 6. Code conversion: BCD ASCII; ASCII Decimal; Decimal ASCII; HEX Decimal and Decimal HEX .

- Programs to generate delay, Programs using serial port and on-Chip timer / counter.

# Note: Programming exercise is to be done on both 8051 & MSP430. II. INTERFACING:

Write C programs to interface 8051 chip to Interfacing modules to develop single chip solutions.

- 8. Simple Calculator using 6 digit seven segment displays and Hex Keyboard interface to 8051.

- 9. Alphanumeric LCD panel and Hex keypad input interface to 8051.

- 10. External ADC and Temperature control interface to 8051.

- 11. Generate different waveforms Sine, Square, Triangular, Ramp etc. using DAC interface to 8051; change the frequency and amplitude.

- 12. Stepper and DC motor control interface to 8051.

- 13. Elevator interface to 8051.

# HDL LAB (Common to EC/TC/IT/BM/ML)

| Sub Code   | : | 10ECL48 | IA Marks          | : | 25 |

|------------|---|---------|-------------------|---|----|

| Hrs/ Week  | : | 03      | <b>Exam Hours</b> | : | 03 |

| Total Hrs. | : | 42      | <b>Exam Marks</b> | : | 50 |

Note: Programming can be done using any compiler. Download the programs on a FPGA/CPLD boards such as Apex/Acex/Max/Spartan/Sinfi/TK Base or equivalent and performance testing may be done using 32 channel pattern generator and logic analyzer apart from verification by simulation with tools such as Altera/Modelsim or equivalent.

# PROGRAMMING (using VHDL /Verilog)

- 1. Write HDL code to realize all the logic gates

- 2. Write a HDL program for the following combinational designs

- a. 2 to 4 decoder

- b. 8 to 3 (encoder without priority & with priority)

- c. 8 to 1 multiplexer

- d. 4 bit binary to gray converter

- e. Multiplexer, de-multiplexer, comparator.

- 2. Write a HDL code to describe the functions of a Full Adder Using three modeling styles.

- 3. Write a model for 32 bit ALU using the schematic diagram shown below A (31:0) B (31:0)

Opcode (3:0)

Enable

- ALU should use combinational logic to calculate an output based on the four bit op-code input.

- ALU should pass the result to the out bus when enable line in high, and tri-state the out bus when the enable line is low.

- ALU should decode the 4 bit op-code according to the given in example below.

| OPCODE | ALU OPERATION |

|--------|---------------|

| 1.     | A + B         |

| 2.     | A - B         |

| 3.     | A Complement  |

| 4.     | A * B         |

| 5.     | A AND B       |

| 6.     | A OR B        |

| 7.     | A NAND B      |

| 8.     | A XOR B       |

- 4. Develop the HDL code for the following flip-flops, SR, D, JK, T.

- 5. Design 4 bit binary, BCD counters (Synchronous reset and Asynchronous reset) and "any sequence" counters

**<u>INTERFACING</u>** (at least four of the following must be covered using VHDL/Verilog)

- 1. Write HDL code to display messages on the given seven segment display and LCD and accepting Hex key pad input data.

- 2. Write HDL code to control speed, direction of DC and Stepper motor.

- 3. Write HDL code to accept 8 channel Analog signal, Temperature sensors and display the data on LCD panel or Seven segment display.

- 4. Write HDL code to generate different waveforms (Sine, Square, Triangle, Ramp etc.,) using DAC change the frequency and amplitude.

- 5. Write HDL code to simulate Elevator operations

- 6. Write HDL code to control external lights using relays.

#### **V SEMESTER**

# MANAGEMENT & ENTREPRENEURSHIP

Subject Code : **10AL51** IA Marks : 25 No. of Lecture Hrs/Week : 04 Exam Hours : 03 Total no. of Lecture Hrs. : 52 Exam Marks : 100

## **MANAGEMENT**

#### UNIT - 1

MANAGEMENT: Introduction - Meaning - nature and characteristics of Management, Scope and functional areas of Management - Management as a Science, Art or Profession Management & Administration - Roles of Management, Levels of Management, Development of Management Thought-Early Management Approaches-Modern Management Approaches.

7 Hrs

## UNIT - 2

**PLANNING:** Nature, importance and purpose of planning process - Objectives - Types of plans (Meaning only) - Decision making - Importance of planning - steps in planning & planning premises - Hierarchy of plans.

6 Hrs

## **UNIT - 3**

**ORGANISING AND STAFFING:** Nature and purpose of organization - Principles of organization - Types of organization - Departmentation - Committees - Centralisation Vs Decentralisation of authority and responsibility - Span of control - MBO and MBE (Meaning only) Nature and importance of Staffing - Process of Selection & Recruitment (in brief).

7 Hrs

# **UNIT - 4**

**DIRECTING & CONTROLLING:** Meaning and nature of directing - Leadership styles, Motivation Theories, Communication - Meaning and importance – Coordination, meaning and importance and Techniques of Coordination. Meaning and steps in controlling - Essentials of a sound control system - Methods of establishing control. **6 Hrs**

# **ENTREPRENEURSHIP**

## **UNIT - 5**

**ENTREPRENEUR:** Meaning of Entrepreneur; Evolution of the Concept, Functions of an Entrepreneur, Types of Entrepreneur, Intrapreneur - an emerging Class. Concept of Entrepreneurship - Evolution of

Entrepreneurship, Development of Entrepreneurship; Stages in entrepreneurial process; Role of entrepreneurs in Economic Development; Entrepreneurship in India; Entrepreneurship – its Barriers. **6 Hrs**

#### **UNIT - 6**

SMALL SCALE INDUSTRY: Definition; Characteristics; Need and rationale: Objectives; Scope; role of SSI in Economic Development. Advantages of SSI Steps to start an SSI - Government policy towards SSI; Different Policies of S.S.I.; Government Support for S.S.I. during 5 year plans, Impact of Liberalization, Privatization, Globalization on S.S.I., Effect of WTO/GATT Supporting Agencies of Government for S.S.I Meaning; Nature of Support; Objectives; Functions; Types of Help; Ancillary Industry and Tiny Industry (Definition only).

## **UNIT - 7**

**INSTITUTIONAL SUPPORT:** Different Schemes; TECKSOK; KIADB; KSSIDC; KSIMC; DIC Single Window Agency: SISI; NSIC; SIDBI; KSFC.

6 Hrs

#### **UNIT - 8**

PREPARATION OF PROJECT: Meaning of Project; Project Identification; Project Selection; Project Report; Need and Significance of Report; Contents; formulation; Guidelines by Planning Commission for Project report; Network Analysis; Errors of Project Report; Project Appraisal. Identification of Business Opportunities - Market Feasibility Study; Technical Feasibility Study; Financial Feasibility Study & Social Feasibility Study.

7 Hrs

#### **TEXT BOOKS:**

- 1.**Principles of Management** P. C. Tripathi, P. N. Reddy; Tata McGraw Hill, 4<sup>th</sup> Edition, 2010

- 2. Dynamics of Entrepreneurial Development & Management Vasant Desai Himalaya Publishing House.

- 3.**Entrepreneurship Development** Small Business Enterprises Poornima M Charantimath Pearson Education 2006.

# **REFERENCE BOOKS:**

- 1. **Management Fundamentals** Concepts, Application, Skill Development Robert Lusier Thomson.

- 2. Entrepreneurship Development S S Khanka S Chand & Co.

- 3. **Management** Stephen Robbins Pearson Education /PHI -17<sup>th</sup> Edition, 2003.

#### DIGITAL SIGNAL PROCESSING

Subject Code : **10EC52** IA Marks : 25 No. of Lecture Hrs/Week : 04 Exam Hours : 03 Total no. of Lecture Hrs. : 52 Exam Marks : 100

## **UNIT - 1**

Discrete Fourier Transforms (DFT): Frequency domain sampling and reconstruction of discrete time signals. DFT as a linear transformation, its relationship with other transforms.

6 Hrs

#### **UNIT - 2**

Properties of DFT, multiplication of two DFTs- the circular convolution, additional DFT properties. 6 Hrs

## UNIT - 3

Use of DFT in linear filtering, overlap-save and overlap-add method.

Direct computation of DFT, need for efficient computation of the DFT (FFT algorithms).

7 Hrs

#### **UNIT - 4**

Radix-2 FFT algorithm for the computation of DFT and IDFT-decimation-in-time and decimation-in-frequency algorithms. Goertzel algorithm, and chirp-z transform. **7 Hrs**

## **UNIT - 5**

IIR filter design: Characteristics of commonly used analog filters – Butterworth and Chebysheve filters, analog to analog frequency transformations. 6 **Hrs**

#### UNIT - 6

Implementation of discrete-time systems: Structures for IIR and FIR systemsdirect form I and direct form II systems, cascade, lattice and parallel realization. **7 Hrs**

## **UNIT - 7**

FIR filter design: Introduction to FIR filters, design of FIR filters using - Rectangular, Hamming, Bartlet and Kaiser windows, FIR filter design using frequency sampling technique.

6 Hrs

#### **UNIT - 8**

Design of IIR filters from analog filters (Butterworth and Chebyshev) - impulse invariance method. Mapping of transfer functions: Approximation of derivative (backward difference and bilinear transformation) method, Matched z transforms, Verification for stability and linearity during mapping

7 Hrs

## **TEXT BOOK:**

1. **Digital signal processing** – **Principles Algorithms & Applications**, Proakis & Monalakis, Pearson education, 4<sup>th</sup> Edition, New Delhi, 2007.

#### REFERENCE BOOKS:

- Discrete Time Signal Processing, Oppenheim & Schaffer, PHI, 2003

- 2. **Digital Signal Processing**, S. K. Mitra, Tata Mc-Graw Hill, 3<sup>rd</sup> Edition, 2010.

- 3. **Digital Signal Processing**, Lee Tan: Elsivier publications, 2007

## **ANALOG COMMUNICATION**

| Subject Code              | : 10EC53 | IA Marks   | : 25  |

|---------------------------|----------|------------|-------|

| No. of Lecture Hrs/Week   | : 04     | Exam Hours | : 03  |

| Total no. of Lecture Hrs. | : 52     | Exam Marks | : 100 |

### **UNIT - 1**

RANDOM PROCESS: Random variables: Several random variables. Statistical averages: Function of Random variables, moments, Mean, Correlation and Covariance function: Principles of autocorrelation function, cross – correlation functions. Central limit theorem, Properties of Gaussian process.

7 Hrs

## **UNIT - 2**

AMPLITUDE MODULATION: Introduction, AM: Time-Domain description, Frequency – Domain description. Generation of AM wave: square law modulator, switching modulator. Detection of AM waves: square law detector, envelop detector. Double side band suppressed carrier modulation (DSBSC): Time-Domain description, Frequency-Domain representation, Generation of DSBSC waves: balanced modulator, ring modulator. Coherent detection of DSBSC modulated waves. Costas loop.

7 Hrs

#### **UNIT - 3**

SINGLE SIDE-BAND MODULATION (SSB): Quadrature carrier multiplexing, Hilbert transform, properties of Hilbert transform, Preenvelope, Canonical representation of band pass signals, Single side-band modulation, Frequency-Domain description of SSB wave, Time-Domain description. Phase discrimination method for generating an SSB modulated wave, Time-Domain description. Phase discrimination method for generating an SSB modulated wave. Demodulation of SSB waves.

6 Hrs

#### **UNIT - 4**

**VESTIGIAL SIDE-BAND MODULATION (VSB):** Frequency – Domain description, Generation of VSB modulated wave, Time - Domain description, Envelop detection of VSB wave plus carrier, Comparison of amplitude modulation techniques, Frequency translation, Frequency division multiplexing, Application: Radio broadcasting, AM radio. **6 Hrs**

#### **UNIT - 5**

**ANGLE MODULATION (FM)-I:** Basic definitions, FM, narrow band FM, wide band FM, transmission bandwidth of FM waves, generation of FM waves: indirect FM and direct FM. **6 Hrs**

#### **UNIT - 6**

**ANGLE MODULATION (FM)-II:** Demodulation of FM waves, FM stereo multiplexing, Phase-locked loop, Nonlinear model of the phase – locked loop, Linear model of the phase – locked loop, Nonlinear effects in FM systems. **7 Hrs**

#### **UNIT - 7**

**NOISE:** Introduction, shot noise, thermal noise, white noise, Noise equivalent bandwidth, Narrow bandwidth, Noise Figure, Equivalent noise temperature, cascade connection of two-port networks.

6 Hrs

# UNIT - 8

NOISE IN CONTINUOUS WAVE MODULATION SYSTEMS: Introduction, Receiver model, Noise in DSB-SC receivers, Noise in SSB receivers, Noise in AM receivers, Threshold effect, Noise in FM receivers, FM threshold effect, Pre-emphasis and De-emphasis in FM,.

7 Hrs

#### **TEXT BOOKS:**

1. **Communication Systems**, Simon Haykins, 5<sup>th</sup> Edition, John Willey, India Pvt. Ltd, 2009.

2. **An Introduction to Analog and Digital Communication**, Simon Haykins, John Wiley India Pvt. Ltd., 2008

## **REFERENCE BOOKS:**

- Modern digital and analog Communication systems B. P. Lathi, Oxford University Press., 4<sup>th</sup> ed, 2010,

- Communication Systems, Harold P.E, Stern Samy and A Mahmond, Pearson Edn, 2004.

- 3. **Communication Systems**: Singh and Sapre: Analog and digital TMH 2<sup>nd</sup>, Ed 2007.

## MICROWAVES AND RADAR

| Subject Code              | : 10EC54 | IA Marks   | : 25  |

|---------------------------|----------|------------|-------|

| No. of Lecture Hrs/Week   | z : 04   | Exam Hours | : 03  |

| Total no. of Lecture Hrs. | : 52     | Exam Marks | : 100 |

#### **UNIT - 1**

MICROWAVE TRANSMISSION LINES: Introduction, transmission lines equations and solutions, reflection and transmission coefficients, standing waves and SWR, line impedance and line admittance. Smith chart, impedance matching using single stubs, Microwave coaxial connectors.

7 Hrs

# UNIT - 2

**MICROWAVE WAVEGUIDES AND COMPONENTS:** Introduction, rectangular waveguides, circular waveguides, microwave cavities, microwave hybrid circuits, directional couplers, circulators and isolators.

6 Hrs

# UNIT - 3 MICROWAVE DIODES.

Transfer electron devices: Introduction, GUNN effect diodes – GaAs diode, RWH theory, Modes of operation, Avalanche transit time devices: READ diode, IMPATT diode, BARITT diode, Parametric amplifiers

Other diodes: PIN diodes, Schottky barrier diodes.

7 Hrs

## UNIT - 4

Microwave network theory and passive devices. Symmetrical Z and Y parameters, for reciprocal Networks, S matrix representation of multi port networks.

6 Hrs

#### **UNIT - 5**

Microwave passive devices, Coaxial connectors and adapters, Phase shifters, Attenuators, Waveguide Tees, Magic tees. **6 Hrs**

#### **UNIT - 6**

**STRIP LINES:** Introduction, Microstrip lines, Parallèle strip lines, Coplanar strip lines, Shielded strip Lines.

6 Hrs

# **UNIT - 7**

**AN INTRODUCTION TO RADAR:** Basic Radar, The simple form of the Radar equation, Radar block diagram, Radar frequencies, application of Radar, the origins of Radar. **7 Hrs**

## **UNIT - 8**

MTI AND PULSE DOPPLER RADAR: Introduction to Doppler and MTI Radar, delay line Cancellers, digital MTI processing, Moving target detector, pulse Doppler Radar. 7 Hrs

## **TEXT BOOKS**:

- 1. Microwave Devices and circuits- Liao / Pearson Education.

- Introduction to Radar systems-Merrill I Skolnik, 3<sup>rd</sup> Ed, TMH, 2001

- 3. **Microwave Engineering** Annapurna Das, Sisir K Das TMH Publication, 2<sup>nd</sup>, 2010.

## **REFERENCE BOOK:**

1. **Microwave Engineering** – David M Pozar, John Wiley India Pvt. Ltd., 3<sup>rd</sup> Edn, 2008.

#### INFORMATION THEORY AND CODING

| Subject Code              | : 10EC55 | IA Marks   | : 25  |

|---------------------------|----------|------------|-------|

| No. of Lecture Hrs/Week   | : 04     | Exam Hours | : 03  |

| Total no. of Lecture Hrs. | : 52     | Exam Marks | : 100 |

### **UNIT - 1**

**INFORMATION THEORY:** Introduction, Measure of information, Average information content of symbols in long independent sequences, Average information content of symbols in long dependent sequences. Markoff statistical model for information source, Entropy and information rate of mark-off source.

7 Hrs

#### **UNIT - 2**

**SOURCE CODING:** Encoding of the source output, Shannon's encoding algorithm. Communication Channels, Discrete communication channels, Continuous channels.

6 Hrs

## **UNIT - 3**

**FUNDAMENTAL LIMITS ON PERFORMANCE:** Source coding theorem, Huffman coding, Discrete memory less Channels, Mutual information, Channel Capacity. 7 Hrs

## **UNIT - 4**

Channel coding theorem, Differential entropy and mutual information for continuous ensembles, Channel capacity Theorem. 6 Hrs

#### **UNIT - 5**

INTRODUCTION TO ERROR CONTROL CODING: Introduction, Types of errors, examples, Types of codes Linear Block Codes: Matrix description, Error detection and correction, Standard arrays and table look up for decoding.

7 Hrs

## **UNIT - 6**

Binary Cycle Codes, Algebraic structures of cyclic codes, Encoding using an (n-k) bit shift register, Syndrome calculation. BCH codes. **6 Hrs**

#### **UNIT - 7**

RS codes, Golay codes, Shortened cyclic codes, Burst error correcting codes.

Burst and Random Error correcting codes.

7 Hrs

#### IINIT - 8

Convolution Codes, Time domain approach. Transform domain approach.

6 Hrs

## **TEXT BOOKS:**

- 1. **Digital and analog communication systems**, K. Sam Shanmugam, John Wiley India Pvt. Ltd, 1996.

- 2. **Digital communication**, Simon Haykin, John Wiley India Pvt. Ltd, 2008.

#### REFERENCE BOOKS:

- 1. **ITC and Cryptography**, Ranjan Bose, TMH, II edition, 2007

- 2. **Digital Communications** Glover and Grant; Pearson Ed. 2<sup>nd</sup> Ed 2008.

## FUNDAMENTALS OF CMOS VLSI

Subject Code : **10EC56** IA Marks : 25 No. of Lecture Hrs/Week : 04 Exam Hours : 03 Total no. of Lecture Hrs. : 52 Exam Marks : 100

#### **UNIT - 1**

**BASIC MOS TECHNOLOGY:** Integrated circuit's era. Enhancement and depletion mode MOS transistors. nMOS fabrication. CMOS fabrication. Thermal aspects of processing. BiCMOS technology. Production of E-beam masks.

3 Hrs

MOS TRANSISTOR THEORY: Introduction, MOS Device Design Equations, The Complementary CMOS Inverter – DC Characteristics, Static Load MOS Inverters, The Differential Inverter, The Transmission Gate, Tristate Inverter.

4 Hrs

#### **UNIT - 2**

**CIRCUIT DESIGN PROCESSES:** MOS layers. Stick diagrams. Design rules and layout – lambda-based design and other rules. Examples. Layout diagrams. Symbolic diagrams. Tutorial exercises. **4 Hrs**

Basic Physical Design of Simple logic gates.

3 Hrs

#### UNIT - 3

CMOS LOGIC STRUCTURES: CMOS Complementary Logic, Bi CMOS Logic, Pseudo-nMOS Logic, Dynamic CMOS Logic, Clocked CMOS Logic, Pass Transistor Logic, CMOS Domino Logic Cascaded Voltage Switch Logic (CVSL).

6 Hrs

### **UNIT - 4**

**BASIC CIRCUIT CONCEPTS:** Sheet resistance. Area capacitances. Capacitance calculations. The delay unit. Inverter delays. Driving capacitive loads. Propagation delays. Wiring capacitances. 3 Hrs

**SCALING OF MOS CIRCUITS:** Scaling models and factors. Limits on scaling. Limits due to current density and noise.

3 Hrs

#### **UNIT - 5**

**CMOS SUBSYSTEM DESIGN:** Architectural issues. Switch logic. Gate logic. Design examples – combinational logic. Clocked circuits. Other system considerations. **5 Hrs**

Clocking Strategies

2 Hrs

UNIT - 6

**CMOS SUBSYSTEM DESIGN PROCESSES:** General considerations. Process illustration. ALU subsystem. Adders. Multipliers. **6 Hrs**

#### UNIT - 7

**MEMORY, REGISTERS AND CLOCK:** Timing considerations. Memory elements. Memory cell arrays. **6 Hrs**

### **UNIT - 8**

**TESTABILITY:** Performance parameters. Layout issues. I/O pads. Real estate. System delays. Ground rules for design. Test and testability.

7 Hrs

### **TEXT BOOKS:**

- CMOS VLSI Design A Circuits and Systems Perspective. 3<sup>rd</sup> Edition. N.H. Weste and David Harris. Addison-Wesley, 2005. (Refer to http://www.cmosvlsi.com)

- 2. **Principles of CMOS VLSI Design: A Systems Perspective**, Neil H. E. Weste, K. Eshragian, and ??? 3<sup>rd</sup> edition, Pearson Education (Asia) Pvt. Ltd., 200?. (Shift to the latest edition.)

- 3. **Basic VLSI Design** Douglas A. Pucknell & Kamran Eshraghian, PHI 3<sup>rd</sup> Edition (original Edition 1994), 2005.

### **REFERENCE BOOKS:**

- 1. R. Jacob Baker. CMOS Circuit Design, Layout and Simulation. John Wiley India Pvt. Ltd, 2008

- Fundamentals of Semiconductor Devices, M. K. Achuthan and K. N. Bhat, Tata McGraw-Hill Publishing Company Limited, New Delhi, 2007.

- 3. **CMOS Digital Integrated Circuits: Analysis and Design**, Sung-Mo Kang & Yusuf Leblebici, 3<sup>rd</sup> Edition, Tata McGraw-Hill Publishing Company Ltd., New Delhi, 2007.

- 4. **Analysis and Design of Digital Integrated Circuits** D.A Hodges, H.G Jackson and R.A Saleh. 3<sup>rd</sup> Edition, Tata McGraw-Hill Publishing Company Limited, New Delhi, 2007.

### DIGITAL SIGNAL PROCESSING LABORATORY

| Subject Code           | : 10ECL57 | IA Marks   | : 25 |

|------------------------|-----------|------------|------|

| No. of Practical Hrs/  | Week: 03  | Exam Hours | : 03 |

| Total no. of Practical | Hrs. : 42 | Exam Marks | : 50 |

## A LIST OF EXPERIMENTS USING MATLAB / SCILAB / OCTAVE / WAB

- 3. Verification of Sampling theorem.

- 4. Impulse response of a given system

- 5. Linear convolution of two given sequences.

- 6. Circular convolution of two given sequences

- 7. Autocorrelation of a given sequence and verification of its properties.

- 8. Cross correlation of given sequences and verification of its properties.

- 9. Solving a given difference equation.

- 10. Computation of N point DFT of a given sequence and to plot magnitude and phase spectrum.

- 11. Linear convolution of two sequences using DFT and IDFT.

- 12. Circular convolution of two given sequences using DFT and IDFT

- 13. Design and implementation of FIR filter to meet given specifications.

- 14. Design and implementation of IIR filter to meet given specifications.

### B. LIST OF EXPERIMENTS USING DSP PROCESSOR

- 1.Linear convolution of two given sequences.

- 2. Circular convolution of two given sequences.

- 3. Computation of N- Point DFT of a given sequence

- 4.Realization of an FIR filter (any type) to meet given specifications .The input can be a signal from function generator / speech signal.

- 5. Audio applications such as to plot time and frequency (Spectrum) display of Microphone output plus a cosine using DSP. Read a way file and match with their respective spectrograms

- 6.Noise: Add noise above 3kHz and then remove; Interference suppression using 400 Hz tone.

- 7.Impulse response of first order and second order system

### **REFERENCE BOOKS:**

- 1.Digital signal processing using MATLAB Sanjeet Mitra, TMH, 2001

- 2.**Digital signal processing using MATLAB** J. G. Proakis & Ingale, MGH, 2000

- 3. Digital Signal Processors, B. Venkataramani and Bhaskar, TMH, 2002

### ANALOG COMMUNICATION LAB + LIC LAB

Subject Code: 10ECL58IA Marks: 25No. of Practical Hrs/Week : 03Exam Hours: 03Total no. of Practical Hrs.: 42Exam Marks: 50

## EXPERIMENTS USING DESCERTE COMPONENTS and LABVIEW - 2009 CAN BE USED FOR VERIFICATION AND TESTING.

- 1. Second order active LPF and HPF

- 2. Second order active BPF and BE

- 3. Schmitt Trigger Design and test a Schmitt trigger circuit for the given values of UTP and LTP

- 4. Frequency synthesis using PLL.

- 5. Design and test R-2R DAC using op-amp

- 6. Design and test the following circuits using IC 555

- a. Astable multivibrator for given frequency and duty cycle

- b. Monostable multivibrator for given pulse width W

- 7. IF amplifier design

- 8. Amplitude modulation using transistor/FET (Generation and detection)

- 9. Pulse amplitude modulation and detection

- 10. PWM and PPM

- 11. Frequency modulation using 8038/2206

- 12. Precision rectifiers both Full Wave and Half Wave.

### VI SEMESTER

### DIGITAL COMMUNICATION

| Subject Code              | : 10EC61 | IA Marks   | : 25  |

|---------------------------|----------|------------|-------|

| No. of Lecture Hrs/Week   | : 04     | Exam Hours | : 03  |

| Total no. of Lecture Hrs. | : 52     | Exam Marks | : 100 |

#### **UNIT - 1**

Basic signal processing operations in digital communication. Sampling Principles: Sampling Theorem, Quadrature sampling of Band pass signal, Practical aspects of sampling and signal recovery. 7 Hrs

### **UNIT - 2**

PAM, TDM. Waveform Coding Techniques, PCM, Quantization noise and SNR, robust quantization. **6 Hrs**

### **UNIT - 3**

DPCM, DM, applications. Base-Band Shaping for Data Transmission, Discrete PAM signals, power spectra of discrete PAM signals. **7 Hrs**

### **UNIT - 4**

ISI, Nyquist's criterion for distortion less base-band binary transmission, correlative coding, eye pattern, base-band M-ary PAM systems, adaptive equalization for data transmission.

6 Hrs

#### UNIT - 5

**DIGITAL MODULATION TECHNIQUES:** Digital Modulation formats, Coherent binary modulation techniques, Coherent quadrature modulation techniques. Non-coherent binary modulation techniques. **6 Hrs**

#### **UNIT - 6**

Detection and estimation, Model of DCS, Gram-Schmidt Orthogonalization procedure, geometric interpretation of signals, response of bank of correlators to noisy input.

6 Hrs

### **UNIT - 7**

Detection of known signals in noise, correlation receiver, matched filter receiver, detection of signals with unknown phase in noise. **7 Hrs**

### **UNIT - 8**

Spread Spectrum Modulation: Pseudo noise sequences, notion of spread spectrum, direct sequence spread spectrum, coherent binary PSK, frequency hop spread spectrum, applications. 7 Hrs

#### **TEXT BOOK:**

Digital communications, Simon Haykin, John Wiley India Pvt. Ltd, 2008.

### **REFERENCE BOOKS:**

- Digital and Analog communication systems, Simon Haykin, John Wildy India Lts, 2008

- 2. **An introduction to Analog and Digital Communication**, K. Sam Shanmugam, John Wiley India Pvt. Ltd, 2008.

- 3. **Digital communications** Bernard Sklar: Pearson education 2007

### **MICROPROCESSOR**

| Subject Code              | : 10EC62 | IA Marks   | : 25  |

|---------------------------|----------|------------|-------|

| No. of Lecture Hrs/Week   | : 04     | Exam Hours | : 03  |

| Total no. of Lecture Hrs. | : 52     | Exam Marks | : 100 |

#### **UNIT - 1**

**8086 PROCESSORS:** Historical background, The microprocessor-based personal computer system, 8086 CPU Architecture, Machine language instructions, Instruction execution timing. **6 Hrs**

### **UNIT - 2**

**INSTRUCTION SET OF 8086:** Assembler instruction format, data transfer and arithmetic, branch type, loop, NOP & HALT, flag manipulation, logical and shift and rotate instructions. Illustration of these instructions with example programs, Directives and operators.

6 Hrs

### **UNIT - 3**

**BYTE AND STRING MANIPULATION:** String instructions, REP Prefix, Table translation, Number format conversions, Procedures, Macros, Programming using keyboard and video display. **7 Hrs**

### UNIT - 4

**8086 INTERRUPTS:** 8086 Interrupts and interrupt responses, Hardware interrupt applications, Software interrupt applications, Interrupt examples.

7 Hrs

### **UNIT - 5**

**8086 INTERFACING:** Interfacing microprocessor to keyboard (keyboard types, keyboard circuit connections and interfacing, software keyboard

interfacing, keyboard interfacing with hardware), Interfacing to alphanumeric displays (interfacing LED displays to microcomputer), Interfacing a microcomputer to a stepper motor.

7 Hrs

### **UNIT - 6**

**8086 BASED MULTIPROCESSING SYSTEMS:** Coprocessor configurations, The 8087 numeric data processor: data types, processor architecture, instruction set and examples. **6 Hrs**

### **UNIT - 7**

**SYSTEM BUS STRUCTURE:** Basic 8086 configurations: minimum mode, maximum mode, Bus Interface: peripheral component interconnect (PCI) bus, the parallel printer interface (LPT), the universal serial bus (USB)

6 Hrs

### **UNIT - 8**

**80386, 80486 AND PENTIUM PROCESSORS:** Introduction to the 80386 microprocessor, Special 80386 registers, Introduction to the 80486 microprocessor, Introduction to the Pentium microprocessor. **7 Hrs**

### **TEXT BOOKS:**

- 4. **Microcomputer systems-The 8086 / 8088** Family Y.C. Liu and G. A. Gibson, 2E PHI -2003

- 5. The Intel Microprocessor, Architecture, Programming and Interfacing-Barry B. Brey, 6e, Pearson Education / PHI, 2003

### **REFERENCE BOOKS:**

- 2. **Microprocessor and Interfacing- Programming & Hardware**, Douglas hall, 2<sup>nd</sup>, TMH, 2006.

- 3. **Advanced Microprocessors and Peripherals** A.K. Ray and K.M. Bhurchandi, TMH, 2<sup>nd</sup>, 2006.

- 8088 and 8086 Microprocessors Programming, Interfacing, Software, Hardware & Applications - Triebel and Avtar Singh, 4e, Pearson Education, 2003

### MICROELECTRONICS CIRCUITS

Subject Code : 10EC63 IA Marks : 25 No. of Lecture Hrs/Week : 04 Exam Hours : 03 Total no. of Lecture Hrs. : 52 Exam Marks : 100

### **UNIT - 1**

MOSFETS: Device Structure and Physical Operation, V-I Characteristics, MOSFET Circuits at DC, Biasing in MOS amplifier Circuits, Small Signal Operation and Models, MOSFET as an amplifier and as a switch, biasing in MOS amplifier circuits, small signal operation modes, single stage MOS amplifiers. MOSFET internal capacitances and high frequency modes, Frequency response of CS amplifiers, CMOS digital logic inverter, detection type MOSFET.

7 Hrs

### UNIT -2

**Single Stage IC Amplifier:** IC Design philiosophy, CoUmparison of MOSFET and BJT, Current sources, Current mirrors and Current steering circuits, high frequency response. **6 Hrs**

### UNIT - 3

**Single Stage IC amplifiers** (continued): CS and CF amplifiers with loads, high frequency response of CS and CF amplifiers, CG and CB amplifiers with active loads, high frequency response of CG and CB amplifiers, Cascade amplifiers. CS and CE amplifiers with source (emitter) degeneration source and emitter followers, some useful transfer parings, current mirrors with improved performance. SPICE examples. **6 Hrs**

### UNIT - 4

**Differences and Multistage Amplifiers:** The MOS differential pair, small signal operation of MOS differential pair, the BJT differences pair, other non-ideal characteristics and differential pair, Differential amplifier with active loads, frequency response and differential amplifiers. Multistage amplifier. SPICE examples.

7 Hrs

### **UNIT - 5**

**Feedback**. General Feedback structure. Properties of negative feedback. Four basic feedback topologies. Series-Shunt feedback. Determining the loop gain. Stability problem. Effect of feedback an amplifier poles. Stability study using Bode plots. Frequency compensation. SPICE examples. **7 Hrs UNIT - 6**

**Operational Amplifiers:** The two stage CMOS Op-amp, folded cascade CMOS op-amp, 741 op-amp circuit, DC analysis of the 741, small signal analysis of 741, gain, frequency response and slew rate of 741. Data Converters. A-D and D-A converters. **6 Hrs**

### **UNIT - 7 & 8**

**Digital CMOS circuits.** Overview. Design and performance analysis of CMOS inverter. Logic Gate Circuits. Pass-transistor logic. Dynamic Logic Circuits. SPICE examples. 12 Hrs

### **Text Book:**

**1. "Microelectronic Circuits",** Adel Sedra and K.C. Smith, 5<sup>th</sup> Edition, Oxford University Press, Interantional Version, 2009.

### **Reference Book:**

- 1. "Fundamentals of Microelectronics", Behzad Razavi, John Wiley India Pvt. Ltd, 2008.

- "Microelectronics Analysis and Design", Sundaram Natarajan, Tata McGraw-Hill, 2007

### **ANTENNAS AND PROPAGATION**

| Subject Code              | : 10EC64 | IA Marks   | : 25  |

|---------------------------|----------|------------|-------|

| No. of Lecture Hrs/Week   | x : 04   | Exam Hours | : 03  |

| Total no. of Lecture Hrs. | : 52     | Exam Marks | : 100 |

### **UNIT - 1**

ANTENNA BASICS: Introduction, basic Antenna parameters, patterns, beam area, radiation intensity, beam efficiency, diversity and gain, antenna apertures, effective height, bandwidth, radiation, efficiency, antenna temperature and antenna filed zones.

7

Hrs

## UNIT - 2

**POINT SOURCES AND ARRAYS:** Introduction, point sources, power patterns, power theorem, radiation intensity, filed patterns, phase patterns. Array of two isotropic point sources. Endfire array and Broadside array. **6 Hrs**

### **UNIT - 3**

**ELECTRIC DIPOLES AND THIN LINEAR ANTENNAS:** Introduction, short electric dipole, fields of a short dipole(no derivation of field components), radiation resistance of short dipole, radiation resistances of

lambda/2 Antenna, thin linear antenna, micro strip arrays, low side lobe arrays, long wire antenna, folded dipole antennas. **7 Hrs**

### **UNIT - 4 & 5**

LOOP, SLOT, PATCH AND HORN ANTENNA: Introduction, small loop, comparison of far fields of small loop and short dipole, loop antenna general case, far field patterns of circular loop, radiation resistance, directivity, slot antenna, Babinet's principle and complementary antennas, impedance of complementary and slot antennas, patch antennas, horn antennas, rectangular horn antennas.

12 Hrs

### **UNIT - 6**

ANTENNA TYPES: Helical Antenna, Yagi-Uda array, corner reflectors, parabolic reflectors, log periodic antenna, lens antenna, antenna for special applications – sleeve antenna, turnstile antenna, omni directional antennas, antennas for satellite antennas for ground penetrating radars, embedded antennas, ultra wide band antennas, plasma antenna, high-resolution data, intelligent antennas, antenna for remote sensing.

8 Hrs

### **UNIT - 7 & 8**

**RADIO WAVE PROPAGATION:** Introduction, Ground wave propagation, free space propagation, ground reflection, surface wave, diffraction.

**TROPOSPHERE WAVE PROPAGATION:** Troposcopic scatter, Ionosphere propagation, electrical properties of the ionosphere, effects of earth's magnetic field.

10 Hrs

### **TEXT BOOKS:**

- 1. **Antennas and Wave Propagation**, John D. Krauss, 4<sup>th</sup> Edn,McGraw-Hill International edition, 2010.

- Antennas and Wave Propagation Harish and Sachidananda: Oxford Press 2007

### **REFERENCE BOOKS:**

- 1. **Antenna Theory Analysis and Design** C A Balanis,  $3^{rd}$  Edn, John Wiley India Pvt. Ltd, 2008

- Antennas and Propagation for Wireless Communication Systems - Sineon R Saunders, John Wiley, 2003.

- Antennas and wave propagation G S N Raju: Pearson Education 2005

#### OPERATING SYSTEMS

| Subject Code         | : 10EC65  | IA Marks   | : 25  |

|----------------------|-----------|------------|-------|

| No. of Lecture Hrs/  | Week: 04  | Exam Hours | : 03  |

| Total no. of Lecture | Hrs. : 52 | Exam Marks | : 100 |

### **UNIT - 1**

### INTRODUCTION AND OVERVIEW OF OPERATING SYSTEMS:

Operating system, Goals of an O.S, Operation of an O.S, Resource allocation and related functions, User interface related functions, Classes of operating systems, O.S and the computer system, Batch processing system, Multi programming systems, Time sharing systems, Real time operating systems, distributed operating systems.

6 Hrs

### **UNIT - 2**

**STRUCTURE OF THE OPERATING SYSTEMS:** Operation of an O.S, Structure of the supervisor, Configuring and installing of the supervisor, Operating system with monolithic structure, layered design, Virtual machine operating systems, Kernel based operating systems, and Microkernel based operating systems. **7 Hrs**

#### UNIT - 3

**PROCESS MANAGEMENT:** Process concept, Programmer view of processes, OS view of processes, Interacting processes, Threads, Processes in UNIX, Threads in Solaris.

6 Hrs

### **UNIT - 4**

**MEMORY MANAGEMENT:** Memory allocation to programs, Memory allocation preliminaries, Contiguous and noncontiguous allocation to programs, Memory allocation for program controlled data, kernel memory allocation.

7 Hrs

### **UNIT - 5**

**VIRTUAL MEMORY:** Virtual memory basics, Virtual memory using paging, Demand paging, Page replacement, Page replacement policies, Memory allocation to programs, Page sharing, UNIX virtual memory.

6 Hrs

### UNIT - 6

**FILE SYSTEMS:** File system and IOCS, Files and directories, Overview of I/O organization, Fundamental file organizations, Interface between file system and IOCS, Allocation of disk space, Implementing file access, UNIX file system. **7 Hrs**

#### **UNIT - 7**

**SCHEDULING:** Fundamentals of scheduling, Long-term scheduling, Medium and short term scheduling, Real time scheduling, Process scheduling in UNIX.

6 Hrs

### **UNIT - 8**

**MESSAGE PASSING:** Implementing message passing, Mailboxes, Inter process communication in UNIX. 7 **Hrs**

### **TEXT BOOK:**

1. "Operating Systems - A Concept based Approach", D. M. Dhamdhare, TMH, 3<sup>rd</sup> Ed, 2010.

### REFERENCE BOOK: